## **APPLICATION NOTE**

# Application information for I<sup>2</sup>C-bus controlled TV Input Processor TDA9321 H AN98072.1

#### **Abstract**

This report gives a description of the TDA9321 H TV Input Processor, together with application aspects.

Purchase of Philips I<sup>2</sup>C components conveys a license under the I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system, provided the system conforms to the I<sup>2</sup>C specifications defined by Philips.

#### © Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copy-right owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

### **APPLICATION NOTE**

# Application information for I<sup>2</sup>C-bus controlled TV Input Processor TDA9321 H AN98072

Author(s):

F. Bremer

T. Bruton

P.C.T.J. Laro

J.F.M. Luijckx

#### Design & Application Department, Consumer Systems Nijmegen, The Netherlands

#### **Keywords**

Vision & Sound IF PLL Synchronization H/V PAL/NTSC/SECAM decoder PALplus helper demodulator Delay line Filters & Switches I<sup>2</sup>C bus controlled

Date: September 1998

#### **Summary**

This report gives a description of the TDA9321 H High end Input Processor together with application aspects. The TDA9321 H is the successor of the TDA914X. It has a higher degree of integration and additional features. The TDA9321 H combines perfectly with the TDA933X H deflection / RGB output processor.

# Philips Semiconductors TDA9321 H **TV Input Processor**

# Application Note AN98072

#### **CONTENTS**

| 1. INTRODUCTION                                          | 9  |

|----------------------------------------------------------|----|

| 2. DEVICE INFORMATION                                    | 11 |

| 2.1 Pinning configuration QFP-64 package                 | 13 |

| 2.2 Device description per functional block              |    |

| 2.2.1 Vision & Sound IF                                  | 16 |

| 2.2.2 Horizontal and vertical synchronization            | 22 |

| 2.2.3 Filters and Switches                               |    |

| 2.2.4 Colour decoder                                     |    |

| 2.2.5 I <sup>2</sup> C bus description                   | 44 |

| 3. APPLICATION INFORMATION                               | 63 |

| 3.1 General                                              |    |

| 3.2 Application remarks per functional block and per pin | 63 |

| 3.2.1 Vision IF & sound IF                               |    |

| 3.2.2 Horizontal and vertical synchronization            | 72 |

| 3.2.3 Filters and Switches,                              |    |

| 3.2.4 Supply, decoupling and grounding                   |    |

| 3.3 Application of non-used pins                         | 85 |

| 4. ALIGNMENTS                                            | 87 |

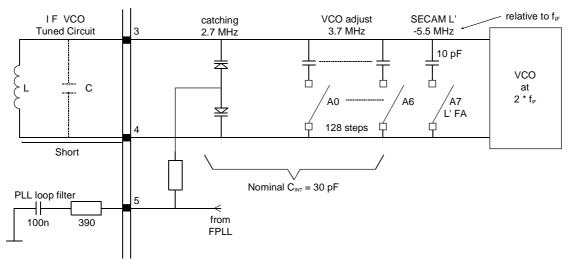

| 4.1 IF-VCO                                               | 87 |

| 4.2 Tuner AGC                                            | 87 |

| 5. REFERENCES                                            | 89 |

# Philips Semiconductors TDA9321 H **TV Input Processor**

# Application Note AN98072

# LIST OF FIGURES

| rig i    | Pinning diagram of QFP-64                                                 | 13 |

|----------|---------------------------------------------------------------------------|----|

| Fig 2    | Video signal for negative and positive modulation                         | 17 |

| Fig 3    | Positive modulated signal with top white reference pulse                  | 18 |

| Fig 4    | Top white and black clamp AGC                                             | 18 |

| Fig 5    | Identification function                                                   | 22 |

|          | PHI-1 Loop                                                                |    |

|          | Sandcastle waveform                                                       |    |

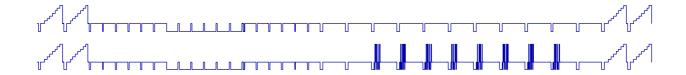

| Fig 8    | Vertical synchronisation, normal (above) and with anticopy signal (below) | 27 |

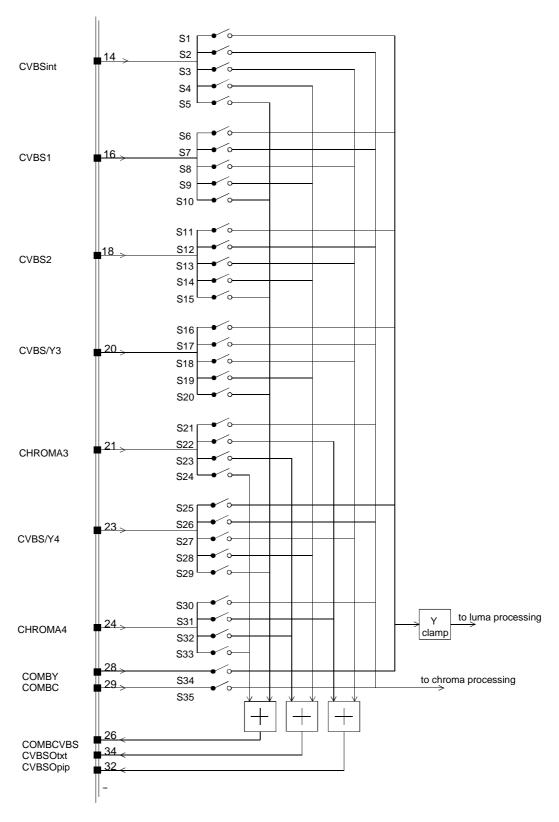

| Fig 9    | Input selection                                                           | 32 |

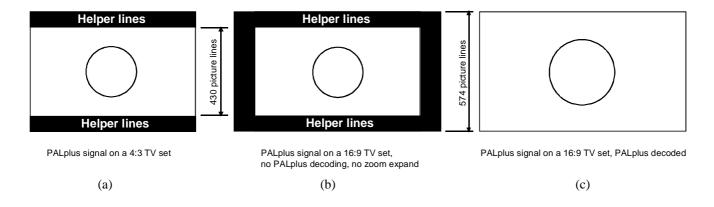

| Fig 10:  | Possible PALplus picture displays                                         | 39 |

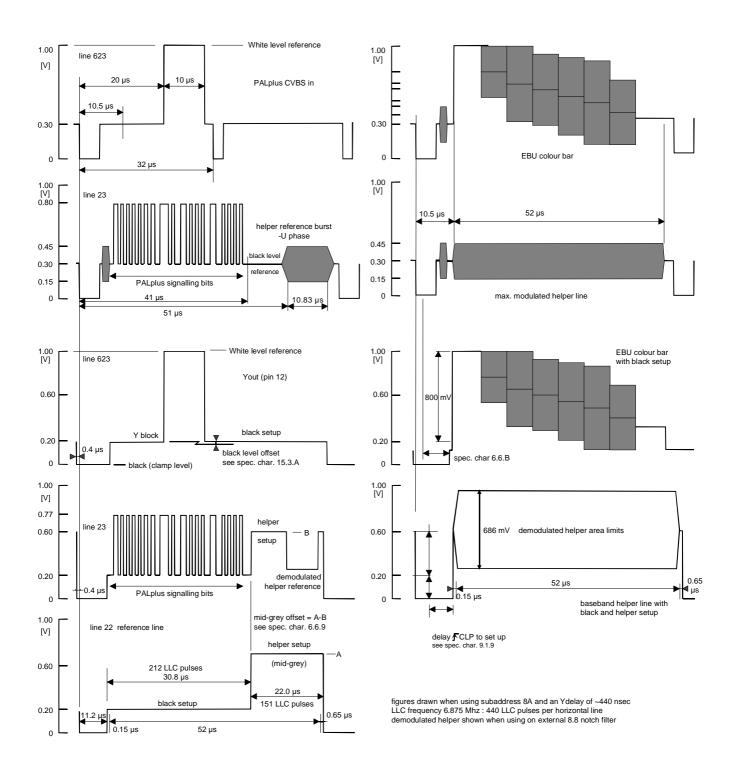

| Fig 11:  | PALplus CVBS input and Y output signals                                   | 41 |

| Fig 12:  | IF-VCO input circuit                                                      | 63 |

| Fig 13:  | Relation ship VCO-capacitors versus VCO-frequency                         | 64 |

| Fig 14:  | PLL-loopfilter versus IF-frequency                                        | 66 |

| Fig 15:  | AFC output bits                                                           | 68 |

| Fig 16:  | Filters to separate QSS/AM signals                                        | 70 |

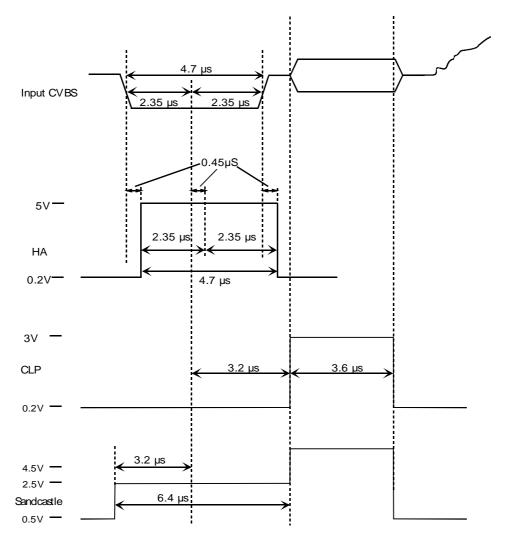

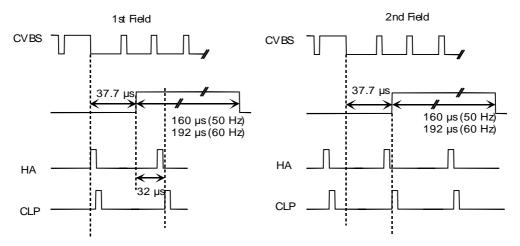

| Fig 17:  | Horizontal timing H <sub>A</sub> /CLP pulse                               | 74 |

| Fig 18:  | Vertical timing H <sub>A</sub> /CLP pulse                                 | 74 |

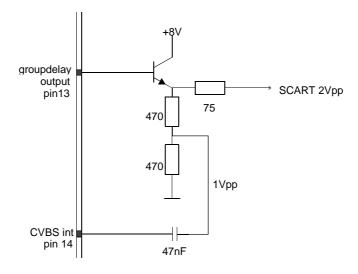

| Fig 19:  | CVBS <sub>INT</sub> signal reduction to 1V at group delay output.         | 75 |

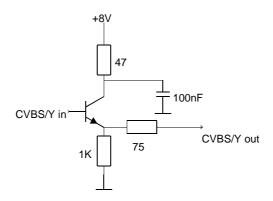

| Fig 20:  | CVBS buffer                                                               | 77 |

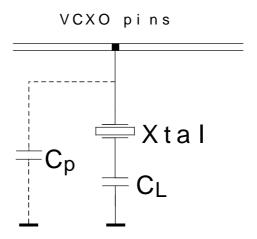

| Fig 21:  | VCXO pin application with parasitic capacitance C <sub>P</sub>            | 81 |

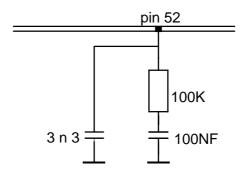

| Fig 22 : | PLL loop filter                                                           | 82 |

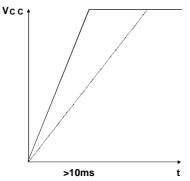

| Fig 23:  | Rise time power supply                                                    | 83 |

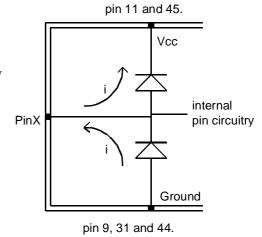

|          | ESD pin protection                                                        |    |

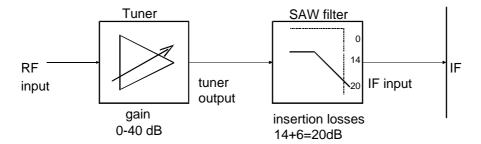

| Fig 25 : | RF to IF signal path.                                                     | 87 |

# ONE CHIP SYSTEM DIAGRAMS

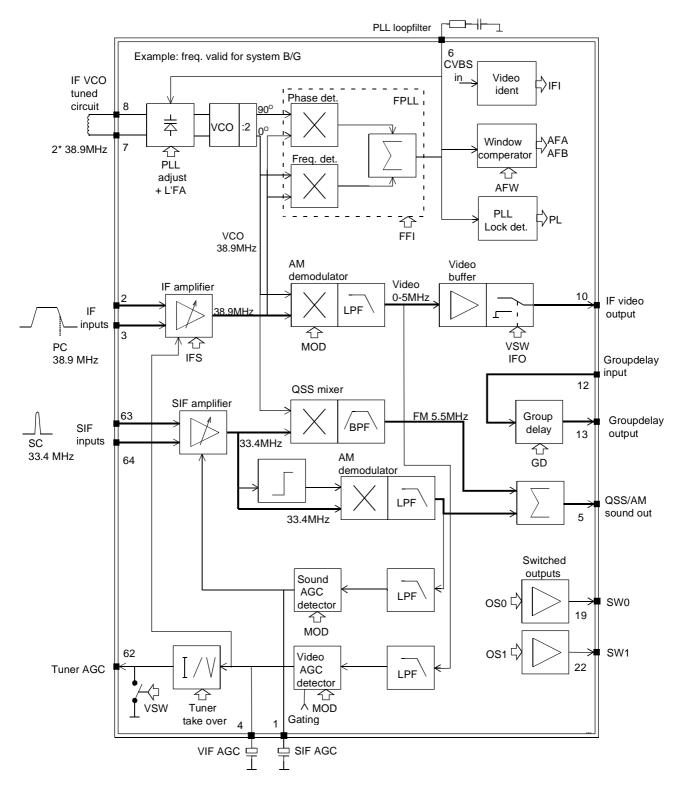

| A 1 : Block diagram: Vision & Sound IF                       |     |

|--------------------------------------------------------------|-----|

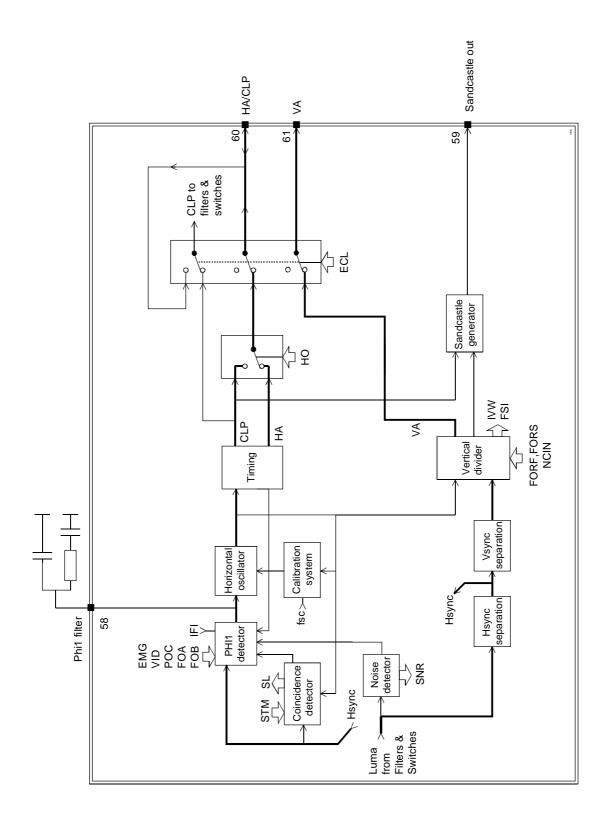

| A 2 : Block diagram: Horizontal and vertical synchronization | 29  |

| A 3 : Block diagram: Filters and Switches                    | 37  |

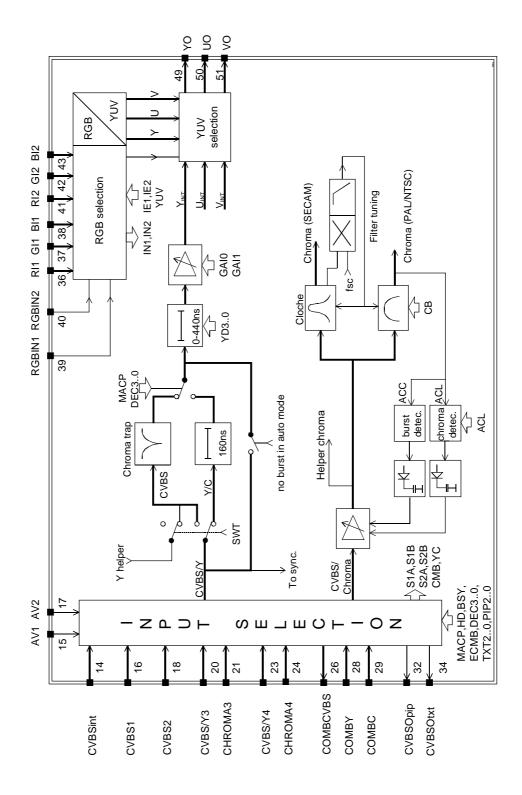

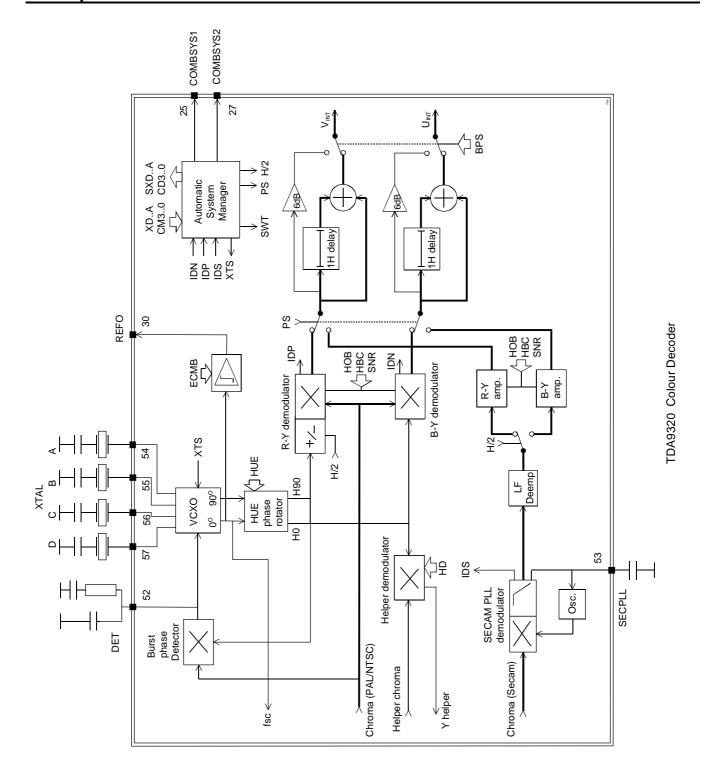

| A 4 : Block diagram: Colour decoder                          |     |

|                                                              |     |

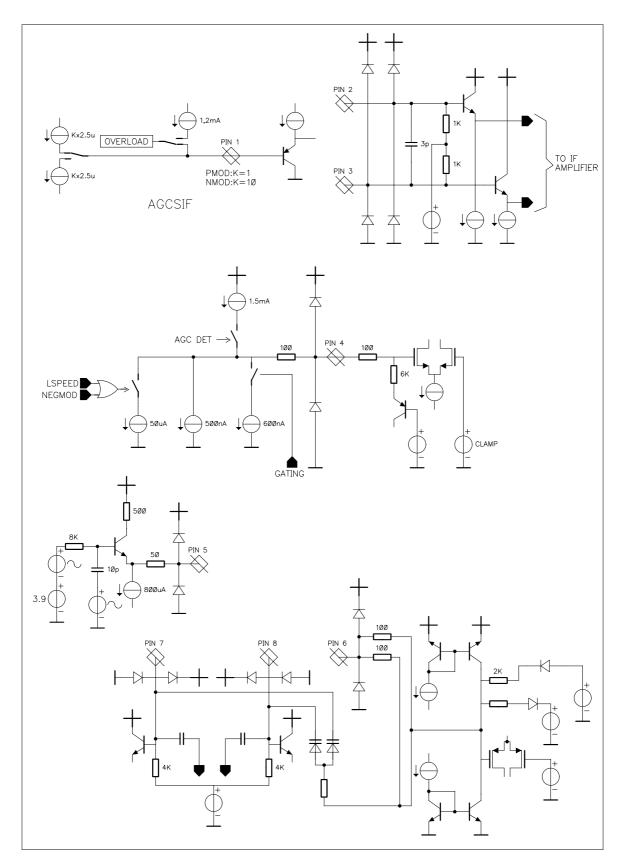

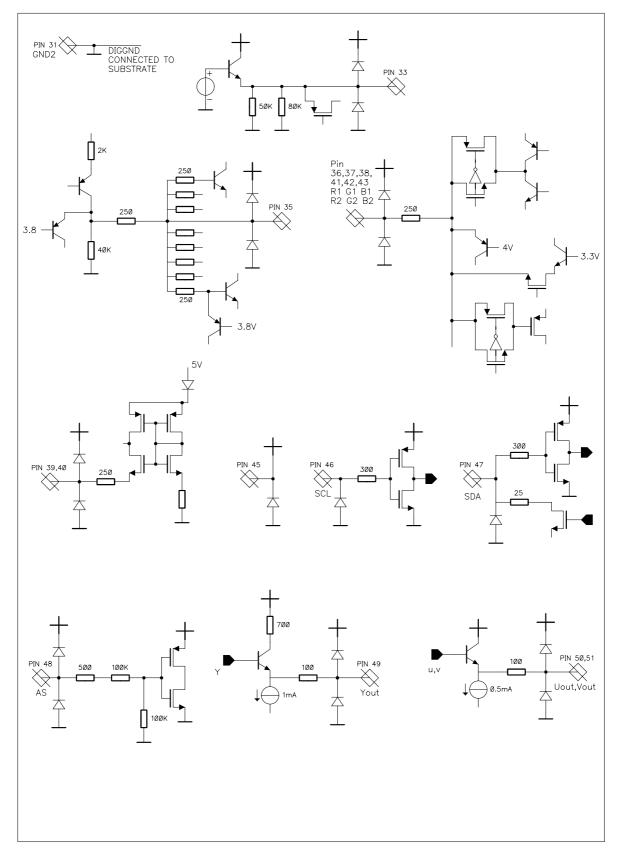

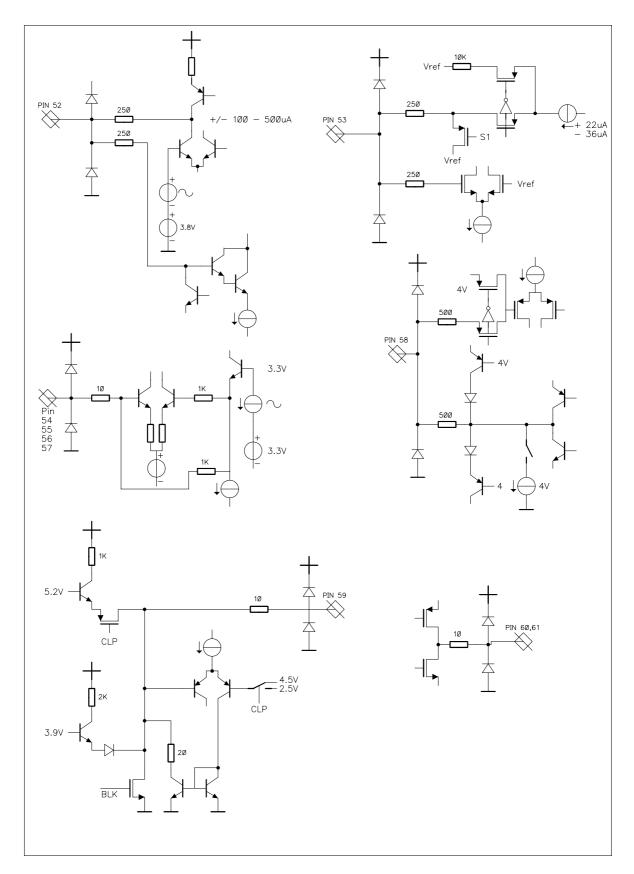

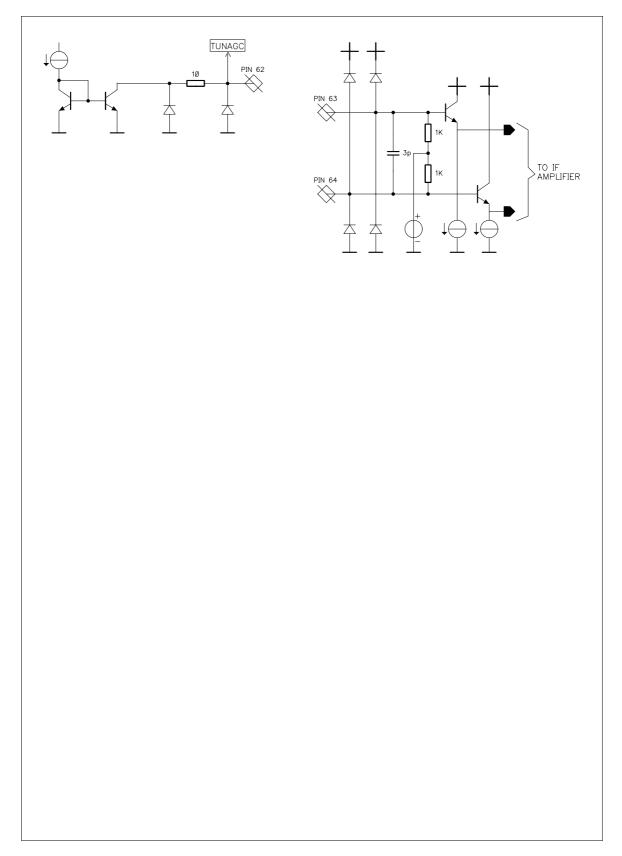

| B 1 : Internal pin configuration (1-8)                       |     |

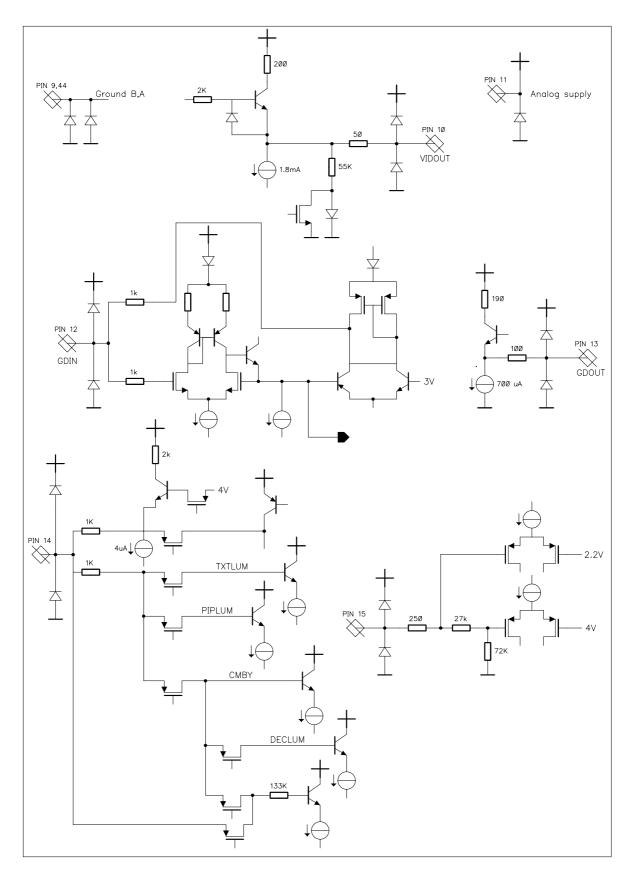

| B 2 : Internal pin configuration (9-15)                      |     |

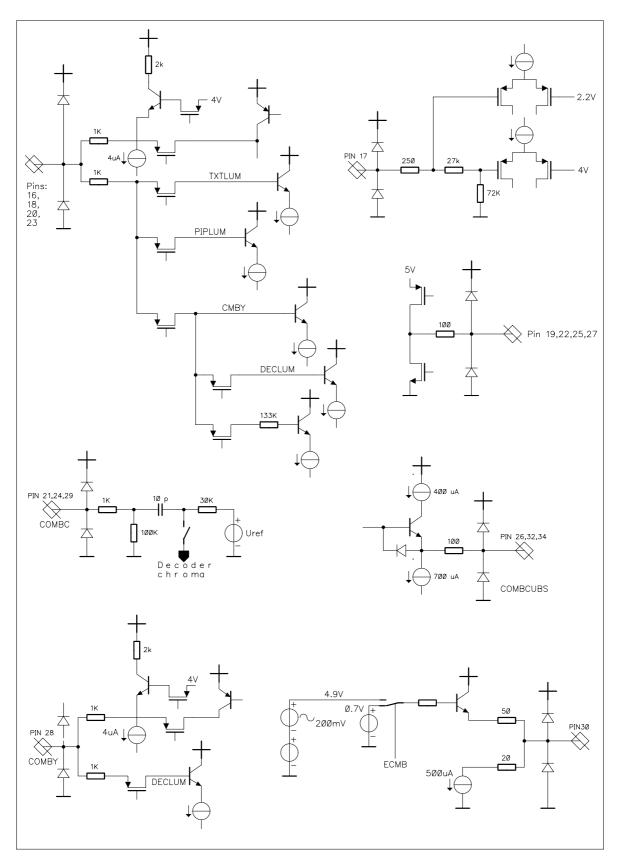

| B 3 : Internal pin configuration (16-30)                     |     |

| B 4 : Internal pin configuration (31-51)                     |     |

| B 5 : Internal pin configuration (52-61)                     |     |

| B 6 : Internal pin configuration (62-64)                     | 101 |

|                                                              |     |

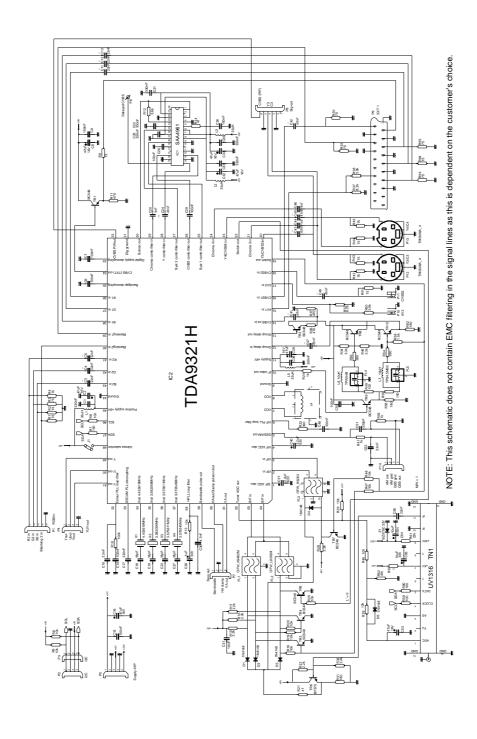

| C 1 : Application diagram for TDA9321 H                      |     |

| •                                                            |     |

|                                                              |     |

| LIST OF TABLES                                               |     |

|                                                              |     |

| Table 1 : Application info per pin number                    | 14  |

| Table 2 : Condition PHI-1 loop                               |     |

| Table 3: PHI-1 time constant selection                       |     |

| Table 4 : SYS1, SYS2 truth table                             |     |

| Table 5 : Input selection possibilities                      |     |

| Table 6 : TXT output selection possibilities                 |     |

| Table 7 : PIP output selection possibilities                 |     |

| Table 8 : Condition PHI-1 loop                               |     |

|                                                              |     |

| Table 9 : IF-VCO tuned circuit data                          |     |

|                                                              |     |

| Table 11 : IF-VCO coil types                                 |     |

| Table 12 : Typical Xtal (Philips)                            |     |

| Table 13 : New series Xtal (Philips)                         |     |

| Table 14: RF to IF signal level.                             | 87  |

Philips Semiconductors

TDA9321 H Application Note AN98072 **TV Input Processor**

#### 1. INTRODUCTION

This report gives a description of the TDA9321 H high end input processor together with application aspects. The TDA9321 H is the successor of the TDA914X family. It has a higher degree of integration and additional features.

The TDA9321 H contains a QSS IF part with video and sound processing (including AM), a very versatile input switch block for CVBS and YC signals, a multistandard colour decoder with integrated baseband delay line, two RGB inputs, horizontal / vertical synchronisation and YUV / synchronisation outputs, all with I²C control. It is designed for use with PAL<sup>plus</sup> processing.

As mentioned, the TDA9321 H also includes the vision-IF part. Compared to a stand alone IC's for vision-IF only the TDA9321 H has the advantage that I<sup>2</sup>C bus commands are available for many control functions and alignment. Optimal performance is achieved by using timing signals which can be derived from the synchronization part.

The number of external components required for application is considerably less than equivalent two or three chip concepts. All necessary alignments can be done via I<sup>2</sup>C control.

The device is optimal for high end applications where many inputs are needed, where processing of YUV signals is needed (e.g. picture improvement, PAL<sup>plus</sup> processing) or the display is running on another frequency (upconversion, 100 Hz or progressive scan).

For these applications a suitable deflection/RGB processor is available, the TDA933X H high end output processor, which matches ideal with the TDA9321 H.

The device is available in QFP 64 (Quad Flat Pack, 64 pins, SOT319-2)

The complete integration of all functions on a single chip has been realised using the BIMOS technology (combined BIpolar and MOS). The high frequent bipolar process is used for video processing like IF vision and various filters. The MOS process is used for all digital parts.

Due to MOS components, it is possible to integrate very large time constants.

| Philips Semiconductors | S |

|------------------------|---|

|------------------------|---|

TDA9321 H

TV Input Processor

Application Note

AN98072

# Application Note AN98072

#### 2. DEVICE INFORMATION

The TDA9321 H is a high end input processor for applications, needing a flexible CVBS/YC input switch block and/or with additional YUV processing. Together with the TDA933X H high end output processor a flexible set architecture can be set up for scan conversion (100 Hz, progressive scan), PAL<sup>plus</sup> decoding etc.

The TDA9321 H includes the video processing from IF to YUV out and QSS IF sound processing for high performance. A versatile CVBS/YC input switch block is included with two independent CVBS outputs, also 2 RGB inputs (or one RGB and one YUV input) are present which are converted to YUV for further processing. The colour decoder is full multistandard including SECAM and Latin America systems and the base band delay line is integrated. The synchronisation part delivers horizontal and vertical synchronisation pulses for further processing. The IC has full  $I^2C$  control for all functions. Only one ( $I^2C$ ) alignment is necessary for the IF PLL.

Below, a survey is given of the main features per functional block:

#### IF

- Vision IF amplifier with high sensitivity and good figures for differential phase and gain

- PLL demodulator with high linearity

- Alignment PLL via I2C

- Multistandard IF with negative and positive modulation, switchable via I<sup>2</sup>C

- Switchable group delay correction circuit which can be used to compensate BG-standard in multi system sets

- Separate SIF input for single reference QSS mode and separate AGC circuit

- AM demodulator without external reference circuit

- 2 universal I<sup>2</sup>C switch outputs, which can be used to switch traps, sound pass filters, etc.

#### Filters and Switches

- Flexible video source select with CVBS input for the internal signal, four external video inputs (two switchable for CVBS or Y/C)

- 2 three-level inputs for indication status level on pin 8 of SCART, level readout via I<sup>2</sup>C

- The output signal of the video source select is externally available (also as CVBS when Y/C input is used)

- Two independent CVBS outputs for PIP, TXT, record out or other purpose (also as CVBS when Y/C input is used)

- Comb filter interface including two control lines for use with TDA4961 combfilter

- 2 linear RGB inputs with fast blanking, one switchable as YUV input, RGB is converted to YUV out

- Standard level YUV output

- Integrated luminance delay line with via I<sup>2</sup>C adjustable delay

- Integrated chroma trap (auto calibrated)

- Integrated chroma bandpass filters with switchable centre frequency (auto calibrated)

- ACC and ACL control

#### Colour decoder

- Full multi system colour demodulator for PAL, NTSC and SECAM with option for 4 X-tals to cover all known colour standards including Latin America.

- Automatic search system for detection of colour standard

- Full PAL plus helper demodulation with correct setups and levels at YUV output

- Optional blanking of "helper" signals for PAL plus and EDTV-2

#### **Synchronisation and Deflection**

- Horizontal synchronisation with PLL control loop and alignment free horizontal oscillator

- Switchable time constants for φ1 (auto or via I<sup>2</sup>C) and switchable macrovision gating

- Horizontal output choice of H<sub>A</sub> pulse related to the synchronisation pulse or CLP pulse related to clamping pulse, also input of external clamp pulse possible

- Vertical count-down circuit for stable behaviour with provisions for non-standard signals

- Vertical output with V<sub>A</sub> pulse for further processing

Application Note AN98072

#### Control

- Full I<sup>2</sup>C bus control, as well for customer controls as for factory alignment

- All automatic control settings have an option for forced mode

#### **Power consumption**

- Low power consumption

#### **Packaging**

- QFP-64 (Quad Flat Pack, 64 pins SOT 319-2)

#### Application

- Small amount of peripheral components compared with competition IC's

#### 2.1 Pinning configuration QFP-64 package

The TDA9321 H is available in Quad Flat Package QFP-64 SOT 319-2.

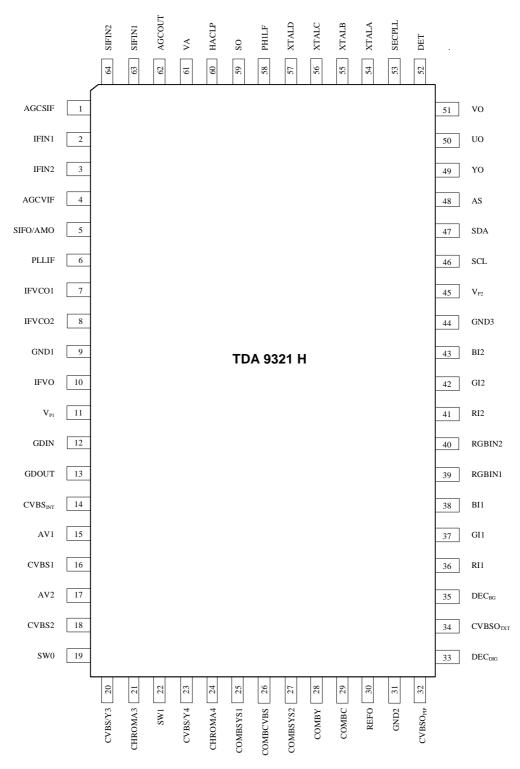

Fig 1 : Pinning diagram of QFP-64

| Philips Semiconductors | S |

|------------------------|---|

|------------------------|---|

TDA9321 H

TV Input Processor

Application Note

AN98072

#### 2.2 Device description per functional block

The TDA9321 H is organised in functional blocks. These different blocks are:

Vision and sound IF Horizontal and vertical synchronisation Filters and Switches Colour decoder and PAL<sup>plus</sup> demodulation Supply decoupling Control I<sup>2</sup>C bus

A description of each functional block has been made together with the corresponding block diagrams.

In the table below, all pin numbers are given with the page number where application information can be found.

| Pin | Page | Pin | Page | Pin | Page | Pin | Page |

|-----|------|-----|------|-----|------|-----|------|

| 1   | 70   | 17  | 77   | 33  | 83   | 49  | 78   |

| 2   | 63   | 18  | 76   | 34  | 76   | 50  | 78   |

| 3   | 63   | 19  | 71   | 35  | 84   | 51  | 78   |

| 4   | 69   | 20  | 76   | 36  | 77   | 52  | 82   |

| 5   | 70   | 21  | 76   | 37  | 77   | 53  | 82   |

| 6   | 69   | 22  | 71   | 38  | 77   | 54  | 79   |

| 7   | 63   | 23  | 76   | 39  | 78   | 55  | 79   |

| 8   | 63   | 24  | 76   | 40  | 78   | 56  | 79   |

| 9   | 84   | 25  | 82   | 41  | 77   | 57  | 79   |

| 10  | 67   | 26  | 76   | 42  | 77   | 58  | 72   |

| 11  | 83   | 27  | 82   | 43  | 77   | 59  | 72   |

| 12  | 67   | 28  | 76   | 44  | 84   | 60  | 73   |

| 13  | 68   | 29  | 76   | 45  | 83   | 61  | 73   |

| 14  | 75   | 30  | 82   | 46  | -    | 62  | 70   |

| 15  | 77   | 31  | 84   | 47  | -    | 63  | 70   |

| 16  | 76   | 32  | 76   | 48  | -    | 64  | 70   |

Table 1 : Application info per pin number

#### 2.2.1 Vision & Sound IF

See also the related block diagram as well as the circuit diagrams at the end of the report.

The main functions are:

- -> Vision IF

- IF amplifier plus AGC and tuner AGC control

- PLL-demodulator and VCO

- Video buffer

- Groupdelay

- Identification for: AFC, Video and PLL-LOCK

- -> Sound IF

- IF amplifier plus AGC

- QSS mixer and AM demodulator

These functions will be described next in this section.

The TDA9321 H includes an integrated vision-IF. Advantages compared to a stand alone IC for vision-IF only are:

- I<sup>2</sup>C bus commands are available for many control functions and alignment. This saves pins and external components.

- Optimal performance is achieved by means of timing/gating signals derived from the synchronization part.

- Build-in accuracy of circuits is derived by use of the available chroma crystal oscillator.

#### \* IF-amplifier

The IF-amplifier has symmetrical inputs and consists of three AC coupled differential gain stages with AGC function. Due to the AC coupling, biasing is simple so that cascades can be used and no DC feedback is necessary. The gain control range of the IF amplifier is 70dB minimal. The input sensitivity for AGC onset is 35  $\mu$ V typical. The maximal IF-gain can be reduced with 20dB by means of I<sup>2</sup>C bus **IFS**. The high frequency range of 32-60MHz makes the amplifier suitable for multistandard application.

#### \* PLL-demodulator and VCO

The IF-signal is demodulated with the help of a PLL detector. The PLL detector is used to regenerate a reference signal that is in phase to the IF-carrier signal. Demodulation is achieved by multiplying this reference signal (that is free from video contents) with the incoming IF-signal.

Switching between positive and negative modulation is done by means of I<sup>2</sup>C bus bit MOD.

A low pass filter after the demodulator output reduces the higher frequency demodulation products.

The voltage controlled oscillator, VCO, makes use of a reference tuned circuit that is connected externally between pins 7 and 8. The VCO is running at the double IF-frequency which prevents self locking of the PLL.

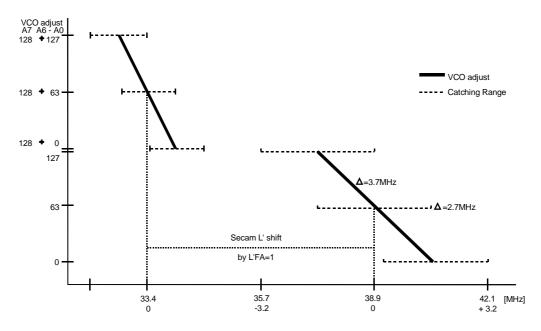

The catching range of the PLL is 2.7MHz. Within this range (and the PLL is in-lock) the performance of the demodulator is independent of the incoming IF-frequency. This automatic tracking is achieved by feedback of the PLL loopfilter voltage to internal varicaps in the VCO.

The VCO does not need an adjustable coil. The VCO frequency can be adjusted fully automatically by I<sup>2</sup>C bus in 128 steps. The resolution is 29kHz/step which gives a tuning range of 3.7MHz.

The frequency adjustment is achieved by internal switchable capacitors at the VCO input.

For SECAM L' a frequency shift can be made of typical -5.5MHz (38.9MHz -> 33.4MHz) by means of I<sup>2</sup>C bus bit **L'FA**. For a correct demodulation, the VCO output frequency is divided by two in order to have the same frequency for both reference and IF-input signal. With the aid of the divider circuit it is also easy to achieve exactly the required 0 and 90 degrees signals.

The PLL loopfilter is connected to pin 6. In order to ensure a fast catching, an acquisition help has been provided by means of the "FPLL", Frequency Phase Lock Loop. This frequency detector gives an output signal to the PLL loopfilter as long as a difference in frequency is detected.

Due to this additional FPPL circuit the loopfilter can be fixed and does not need to be switchable.

The PLL loopfilter time constant can be made fast via Fast Filter IF-PLL, **FFI.** This function has been made available to handle RF-transmitter signals with large phase modulation (for special market areas).

#### \* Video buffer

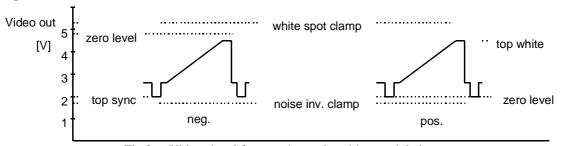

The video buffer is required to provide a low ohmic video output with the right amplitude and to protect this output for the occurrence of noise peaks, refer to figure below. The video buffer also contains a level shifter and gain stage for positive and negative modulation in order to provide a correct video amplitude and DC level.

The video buffer bandwidth is typical 9 MHz. The video output amplitude is 2.5Vpp (sync inclusive), independent of the supply voltage.

A white spot clamp prevents the video amplitude becoming greater than 6.0V typical.

A noise clamp prevents the video output becoming less than 1.5V typical. (Top sync is approx. 2V) For strong signal only, the noise peak is inverted to black level 2.7V.

Fig 2 : Video signal for negative and positive modulation

The IF part can be switched-off by means of I<sup>2</sup>C bus command **VSW**. The internal CVBS input than can be used (with minimum components) as external input, for instance for satellite. By means of **IFO** the IF-part can be made currentless for minimal dissipation.

#### \* AGC

An AGC system controls the IF amplifier gain such that the video output amplitude is constant.

The demodulated video signal is supplied, via a low pass filter, to an AGC detector with external decoupling capacitor. The AGC detector voltage controls directly the IF gain stages.

#### Negative/positive modulation:

For optimal AGC behaviour the charge and discharge current of the AGC are chosen so that both, a relative fast AGC, as well a low tilt are possible for positive and negative modulated signals with the same AGC capacitor. A SECAM-L speed-up circuit improves the AGC settling time after IF-signal loss.

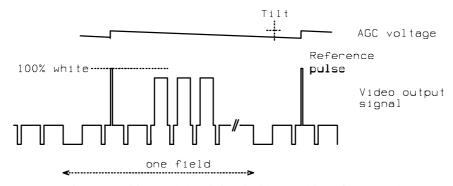

With tilt is mend the video amplitude variation due to less "memory" function of the AGC capacitor). In Fig 3 the tilt is given during a field period for positive modulated signals. For negative modulated signals the tilt is line frequent. For negative modulated signals the AGC is a top sync detector.

#### Positive modulation:

For positive modulated signals the AGC is a <u>top white AGC including black level clamp</u> which making the video amplitude independent of video contents.

A top white AGC requires a 100% white reference pulse in order to be independent of video contents. Suitable for that purpose is the white pulse (Video Insertion Test Signal, VITS) in line 17 and 330 - see Fig 3.

Because the time constant is large (AGC current is decreased for positive modulation) the AGC will be independent of the video contents between the reference pulses.

The maximum tilt per field is defined by the external capacitor, the AGC steepness and the small discharge current in this mode.

Fig 3 : Positive modulated signal with top white reference pulse

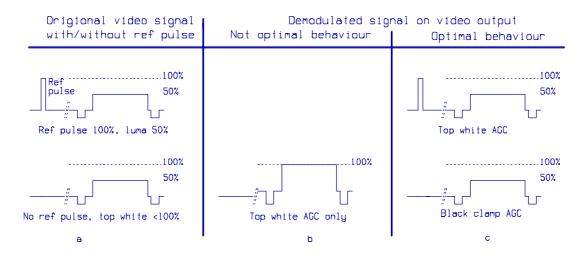

This top white AGC however is not optimal for those signals that have neither a white reference pulse or white video information (e.g. with some VCR signals). Due to the top level AGC principle a gray scene becomes white and a dark scene becomes gray, see Fig 4. This behaviour can be avoided by means of the black level clamp.

Fig 4: Top white and black clamp AGC

The Fig 4 "b" shows that the video amplitude is increased by the top white AGC, such that 100% white is obtained. As a consequence the black level increases also.

The black level clamp AGC in "c" prevents this behaviour and becomes automatically active if the video black level on the video output increases.

Application Note AN98072

In the external mode only the top white AGC is active. The black clamp AGC than is switched off because the internal signal is not synchronised any more to the horizontal oscillator.

#### SECAM-L speed-up circuit:

In case of positive modulation and large reduction of the incoming IF-input level a speed-up circuit is needed. This because the AGC action is slow since the AGC discharge current is small (450nA), for minimizing the tilt.

The speed-up circuit measures the amplitude of the video output signal and will react after approximately 60ms if the video output is continuously below 80% white level.

If the speed-up is activated the AGC capacitor will be discharged with a current of 50uA.

#### \* Tuner AGC

The tuner AGC is provided to reduce the tuner gain and thus the tuner output voltage when receiving strong RF signals. The tuner AGC takes over when the IF input reaches a certain input level, that can be adjusted by I<sup>2</sup>C function **AGC take over**. The tuner gain can be reduced by means of the open collector output pin 62.

#### \* AFC

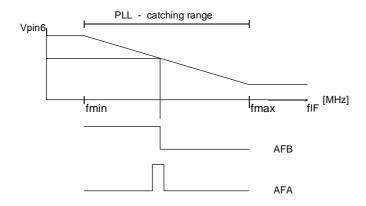

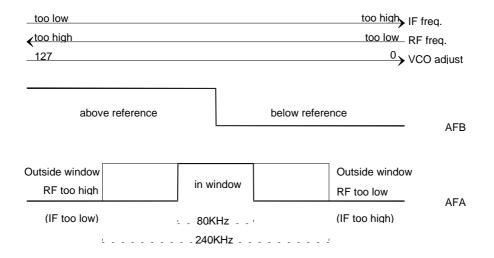

The PLL loopfilter voltage is inverse proportional to the frequency of the incoming IF-frequency, see Fig 15. For this reason the loopfilter voltage can be used for AFC information. The "analogue AFC" voltage is amplified and fed to a window comparator. The AFC output is available by the I<sup>2</sup>C bus outputs **AFA**, **AFB**. The AFC window width can be increased by means of I<sup>2</sup>C bus **AFW**. Search tuning can be done with different frequency steps.

Due to the use of PLL detector, the AFC information is independent from video contents. Notice that the AFC information is only valid when the PLL is in-lock, thus **PL**=1.

#### \* Video identification

The IF-part includes a stand alone video identification circuit, independent of the sync part. The ident output is available by I<sup>2</sup>C bus, **IFI**, and can be used during search tuning and for automatic sound mute in full scart application. The video ident circuit measures the main frequency of the input signal which should be approximately 16kHz.

The video ident can be connected to the "internal" video signal/ or to the selected CVBS input signal. See Fig 5.

#### \* PLL-LOCK identification

The TDA9321 H provides a new identification bit that indicates whether the IF-PLL is inlock. This bit can be used to optimise the search tuning algorithm.

#### \* Group delay

The TDA9321 H contains a group delay correction circuit which can be switched between system BG and flat group delay response charactersistic. This has the advantage that in multi-standard receivers no compromise has to be made for the choice of the SAW filter. Both the input and output of the group delay correction circuit are externally available so that the sound trap can be connected between the IF video output and group delay correction input. The output signal of the correction circuit can be supplied to the video processing circuit and the SCART plug.

#### \* Sound circuit

The TDA9321 H allows quasi split sound applications for an FM and AM output signal.

The sound IF amplifier is identical to the vision IF amplifier. The AGC is related to the SIF carrier levels (average level of AM or FM carriers) and ensures a constant signal amplitude of the AM demodulator and the QSS mixer. The AGC time constant is automatically adapted for positive and negative modulation (AGC is slow and fast respectively).

The single reference QSS mixer is realised by a multiplier. In this multiplier the SIF signal is converted to the intercarrier frequency by mixing it with the regenerated picture carrier from the VCO. The mixer output signal is supplied to the output via a high pass filter for attenuation of the residual video signals. With this system a high performance stereo sound processing can be achieved.

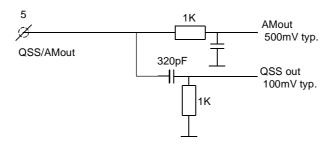

The AM sound demodulator is realised by a multiplier. The modulated sound IF signal is multiplied in phase with the limited SIF signal. The demodulator output is supplied to the output via a low-pass filter for attenuation of the carrier harmonics. Both QSS and AM signals are available at one output pin.

Application Note AN98072

#### \* Switched outputs

The TDA9321 H has two I2C bus controlled (**OS0, OS1**) output ports which can be used to switch sound traps, SAW filters or other external components.

A 1: Block diagram: Vision & Sound IF

#### 2.2.2 Horizontal and vertical synchronization

See also the related block diagram as well as the diagrams at the end of the report.

The main functions are:

- \* Horizontal sync separator

- \* Horizontal oscillator and calibration system

- \* PHI-1 detector and PLL loop

- \* Horizontal output

- \* Coincidence detector

- \* Noise detector

- \* Vertical sync separator

- \* Vertical divider system

- \* Vertical output

Before describing the functional blocks, first the various identification signals are discussed. They play an important role in the sync system behaviour and knowing their working and interrelations helps to better understand the sync system behaviour.

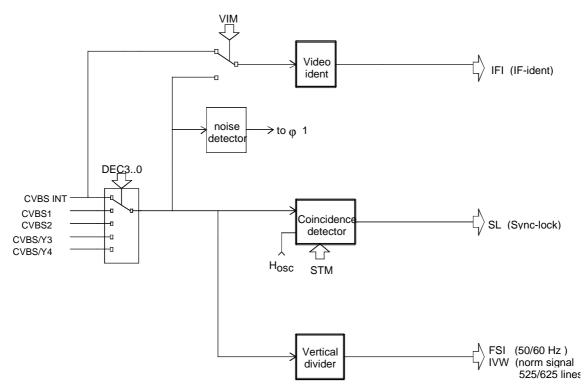

#### \* Identification signals

The video processor includes several identification circuits. There are a number of identification signals, generated by other blocks, which influence the synchronisation behaviour. Also there are identification signals, generated by the sync block itself, which are partly used inside the sync block and/or are meant for use by other blocks. See both Fig 5 below and Fig 6.

Fig 5 : Identification function

# Application Note AN98072

- Video ident: identifies a line frequent video signal.

The output IFI (Video Ident) can be used for:

- search tuning. For reliable transmitter detection, **IFI** should be used together with **SL** and **IVW** (see coincidence detector and vertical divider section below).

- switching automatically the PHI-1 for stable OSD (On Screen Display) at no signal (when **VID**, video ident enable, is low)

- switching the PHI-1 for very stable OSD/Blue Mute using **POC** (PHI-1 off, detecting signal with **IFI**)

With **VIM** (Video ident mode) the video ident **IFI** can be connected to either the internal CVBS input (IF) pin 14 or the output of CVBS switches (selected source).

- Coincidence detector: in-lock detection of the horizontal oscillator.

The output **SL** (Sync lock) can be used for:

- search tuning. Also here for reliable transmitter detection, **SL** can be used together with **IVW** (see vertical divider section below).

- out of-lock information to be displayed via OSD

- automatic switching the PHI-1 for fast catching

The sensitivity of SL can be reduced (about 5 dB) with control bit STM (Search Tuning Mode). This can prevent too many false stops during search tuning.

The main difference using **SL** or **IFI**:

- **SL** sensitivity and reliability is better than **IFI**. When IFI is used for signal identification, it is advised to check **SL** before taking important decisions like storing transmitters and muting displayed video or sound. Also for maximum sensitivity during search tuning, it is best to use **SL**.

- **IFI** can be used to monitor the incoming signal from IF independent of the chosen source (useful for keeping tuned and/or muting CVBS tuner out for SCART application.). **SL** is always related to the displayed signal.

- **IFI** is also available to detect a valid signal when the PHI-1 loop is completely switched off using **POC** (**SL** is not valid then) e.g. when a company logo is displayed at no signal condition.

#### - Vertical divider:

Two output signals are available: FSI (50/60Hz indication) and IVW:

- **FSI** gives the vertical divider mode: 50 or 60Hz, useful for correct OSD positioning on screen.

- **IVW** becomes high when video signals are detected with a line number between 522 528 or 622 628 per frame indicating a signal near or fulfilling the TV norm. **IVW** can be used together with **IFI** or **SL** during search tuning to decide whether data is to be stored.

#### - Miscellaneous:

- Noise detector: Connected to the selected video source. Used to switch the PHI-1 time constant. See separate function description.

#### \* Main function description

Next, the main functions for sync will be described.

#### \* Horizontal sync separator

The horizontal sync separator is supplied from the CVBS/Y inputs (chosen video source). For horizontal synchronisation the sync separator slices in the middle of the sync pulse and the slicing level is independent of the sync pulse amplitude. For the vertical synchronisation the sync pulse is sliced at a level of about 30% (closer to the black level). This ensures optimal output signals for a stable horizontal and vertical deflection under various video input conditions.

The top sync level is clamped at the CVBS input. The black level is stored internally.

#### \* Horizontal oscillator and calibration system

The horizontal oscillator requires no external components and is fully integrated. The adjustment for nominal frequency is derived automatically by a calibration circuit.

The oscillator runs at a frequency of 440 Fh (440 \* 15625 = 6.875 MHz). This oscillator signal is used via a divider chain to derive several other gating and timing signals.

After calibration the horizontal oscillator is controlled by the PHI-1 loop for synchronisation with the incoming video input signal.

The calibrator is responsible for the automatic adjustment of the horizontal oscillator. One of the colour crystals is being used as reference. For that reason a correct setting by XD..XA (Xtal definition) is very important.

Calibration occurs during the vertical retrace period and <u>only</u> under following conditions:

- At power-on/initialisation (POR = 1)

- After power dip (shutdown detection), re-initialisation is required. (POR = 1)

- After loss of synchronisation (e.g. after channel switching)

Note that after power-on, the  $H_A/CLP$  output pulses are suppressed till calibration has taken place, i.e. till after **POR** becomes 0, all  $I^2C$  registers have been written and calibration was succesful.

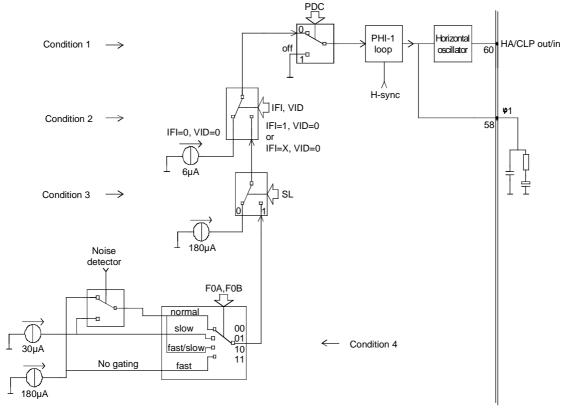

#### \* PHI-1 detector

The PHI-1 detector is a PLL circuit that synchronises the horizontal oscillator with the incoming video signal. The PLL compares the output of the H-sync separator with the horizontal oscillator. The PLL output current is converted to a voltage by means of the external loop filter. This voltage controls the horizontal oscillator. The loop filter is connected externally so the time constant can be defined according to the customer requirements. Because the static loop gain is very high there will be no phase shift when switching between input signals with different line frequencies (e.g. Fh with 50 and 60 Hz. systems). Following figure gives the functions that are effecting the PHI-1 loop time constant.

Fig 6: PHI-1 Loop

Following conditions can be distinguished, see table below.

|   | Condition PHI-1 loop      | Control bit via I <sup>2</sup> C                                                               | Function suitable for:                            |

|---|---------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1 | Completely off            | POC set to 1 (use IFI or external ident circuit to detect valid incoming signal, SL not valid) | Very stable OSD, Blue Mute                        |

| 2 | Very slow                 | IFI reads 0, VID set to 0                                                                      | Stable OSD during search                          |

| 3 | Out-lock                  | SL reads 0                                                                                     | Automatic fast settling PHI-1                     |

| 4 | In-lock, normal operation | FOA/FOB                                                                                        | 4 time constants available for optimal for TV/VCR |

Table 2 : Condition PHI-1 loop

For normal in-lock operation, condition 4, the PHI-1 time constant can be selected by **FOA/FOB**. In practice, three of the four settings are practical to use. Following table explains the three relevant **FOA/FOB** settings. Below the table, some suggestions are given how to use these functions.

| FO | <b>COA/FOB</b> PHI-1 time constant PHI-1 gating |                       | PHI-1 gating      | Suitable for:                                                                                                                        |

|----|-------------------------------------------------|-----------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0                                               | Fast/slow (1), "auto" | yes, in slow only | Off air reception + VCR via antenna <sup>(2)</sup> (compromise)<br>Ext.input for general use <sup>(2)</sup> (VCR, CD-I,descramblers) |

| 1  | 0                                               | Fast/slow (1)         | yes               | Off air reception only, high noise immunity (gating)                                                                                 |

| 1  | 1                                               | Fast                  | no                | Special VCR program number ("0") External input, optimal for VCR, CD-I                                                               |

Table 3 : PHI-1 time constant selection

- (1) Fast or slow depends on whether the noise detector is activated.

- (2) Not suitable for weak VCR signals via antenna (this due to active gating in the slow mode).

#### Normal off-air reception conditions or cable:

- Use **FOA/FOB** = 0 0 for program numbers. VCR reception via antenna possible on all program numbers.

- Use **FOA/FOB** = 1 1 for external input (VCR, CD-I)

#### <u>Difficult off-air reception conditions (weak signal and/or interference):</u>

- Use **FOA/FOB** = 1 0 for program numbers (optimal off-air reception due to gating)

- Use **FOA/FOB** = 1 1 for special program number (program 0) for VCR reception via antenna

- Use **FOA/FOB** = 1 1 for external input (VCR, CD-I)

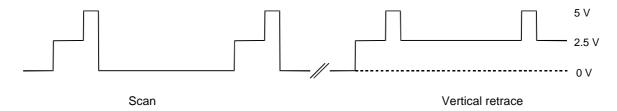

#### \*Sandcastle

The synchronisation part generates a 2-level sandcastle pulse. Normal the output level is low, during horizontal and vertical blanking it is 2.5 V typical and during burstkey 5 V typical. See the figure below.

Fig 7 : Sandcastle waveform

The sandcastle can be used by external IC's for horizontal and vertical blanking, clamping synchronised signals on the backporch and keying out the burstkey of synchronised CVBS signals.

#### \* Horizontal input/output

The H<sub>A</sub>/CLP pin 60 can be used as in- or output:

Output function, internal clamp mode

This mode is selected when  $\mathbf{ECL} = 0$ . Horizontal pulses are provided at pin 60 which can be used for synchronisation of further processing of the YUV outputs and synchronisation of the deflection drive for the display.

Two pulses are available, H<sub>A</sub> and CLP, the selection is made with the bit **HO**:

- CLP pulse ( $\mathbf{HO} = 0$ )

- This pulse has the same timing as the burstkey/clamping pulse on the sandcastle and has a typical width of 3.6 μs..

- $H_A$  pulse (**HO** = 1)

The timing of  $H_A$  is the same as the incoming sync pulse of the selected CVBS/Y signal, with some delay (0.45  $\mu$ s) due to the low pass filter in the sync seperator part. The typical width is 4.7  $\mu$ s.

Both pulses are positive, the low level is typical 0.2 Volt and the high level 5 Volt.

The two pulses give maximum flexibility for further processing like deflection processors (e.g. TDA 9150/51), combined RGB output/deflection processors (e.g. TDA 933X H) and scan conversion boxes like 100 Hz or progressive scan. After power-on, the  $H_A$ /CLP output pulses are suppressed until calibration of the horizontal oscillator has taken place, see "horizontal oscillator and calibration system".

#### Input function, external clamp mode

This mode is meant for insertion of YUV/RGB signals, accompanied by suitable positive horizontal (clamp) and vertical timing pulses. In this way, it is not needed to feed a synchronised composite sync signal to one of the CVBS/YC inputs. By setting ECL = 1, pin 60 is switched to high ohmic input and at the same time the vertical pulse  $V_A$  at output pin 61 is suppressed. In this external clamp mode it is possible to feed an external clamp pulse to pin 60. This external clamp pulse is then used internally for all clamping actions at both YUV/RGB inputs. The timing of this pulse should therefore be correct with respect to the applied YUV/RGB signals at the inputs and regarding timing preferably be comparable with the internal generated CLP pulse.

The external clamp pulse should be positive, the input can interface with all standard 5 Volt logic outputs.

In external mode, the external offered clamp pulse should also be used for further processing of the YUV outputs. So when this mode is used, it is logical to select for internal mode also the CLP pulse as output pulse. Because also the vertical  $V_A$  pulse is suppressed, an external vertical pulse should be provided if this is necessary for further processing.

Application Note AN98072

#### \* Noise detector

The synchronisation circuit has an internal noise detector. If the PHI-1 **FOA/FOB** is set to 0 0 (Automatic mode) or 1 0 (Gated mode) the noise detector is used to switch the time constant of the horizontal PLL. The input of the detector is connected to the selected CVBS/YC input.

The noise detector measures the RMS value of the noise during a part of the sync pulse. (The detection level is 100mVrms and corresponds to 20dB S/N-ratio for 1Vpp CVBS).

A field counter is used for hysteresis and decides after 2 successive fields whether noise is detected. When noise is detected the horizontal PLL time constant is switched to slow.

The output of the noise detector is also available via **SNR**, when the signal to noise ratio becomes less than 20 dB, **SNR** becomes 1.

#### \* Coincidence detector (Synchronisation Lock SL)

The coincidence detector detects whether the incoming CVBS signal is synchronised with the horizontal oscillator, thus whether the PHI-1 loop is in-lock. The output is available by I<sup>2</sup>C bus, SL, and can be used for search tuning and OSD. In automatic mode (FOA/FOB = 00) the coincidence detector switches for out of lock condition the PHI-1 loop to fast to ensure fast horizontal catching. During search tuning the coincidence detector can be made less sensitive (about 5 dB) by control bit STM (search tuning mode). This prevents false stops.

#### \* Vertical sync separator

The vertical sync separator separates the vertical sync pulse from the composite sync signal. This separated sync pulse is used to trigger the vertical divider system. To generate a trigger pulse for the divider the minimum pulse width of the incoming vertical sync pulse must be 17µs.

The integrator network is designed such that for anticopy signals (e.g. Macrovision) with vertical pulses of  $10\mu$ s (on) and  $22\mu$ s (off) still a vertical sync pulse is generated. (Because more lines with vertical pulses are present, pulse width of less than  $17\mu$ s is allowed, by integration still the required level is reached).

To improve the behaviour for such anticopy signals, an extra gating function is implemented to prevent disturbance of the PHI-1 loop during these extra vertical pulses. This gating function can be enabled by setting  $\mathbf{EMG} = 1$  and is only active under the following conditions:

- **EMG** = 1 (Macrovision gating enabled)

- **SL** = 1 (valid signal present)

- **IVW** = 1 (Norm or near norm signal detected, 522-528/622-628 lines/frame)

Fig 8 : Vertical synchronisation, normal (above) and with anticopy signal (below)

# Application Note AN98072

#### \* Vertical divider system

The divider system uses a counter that delivers the timing for the vertical pulse at the VA output pin 61 The clock is derived from the horizontal line oscillator.

The divider system synchronizes on the vertical sync pulse of the vertical sync separator.

The divider has three modes of operation:

#### 1 Search mode (large window)

This mode is activated when the circuit is not synchronized or when a non-standard signal is received. In the search mode the divider can catch between about 45 and 64.5Hz.

#### 2 Standard mode (narrow window)

This mode is switched on (coming from search mode) when more than 15 successive vertical sync pulses are detected in the narrow window. When the circuit is in the standard mode and a vertical sync pulse is missing the retrace of the vertical ramp generator is started at the end of the window (thus automatic insertion of missing vertical sync pulses). As consequence the disturbance of the picture is very small. The circuit will switch back to the search window when 6 succeeding vertical periods no sync pulses are found within the window. (See also **NCIN** below)

In the narrow window mode the PHI-1 is inhibited during the vertical egalization pulses to prevent disturbance.

#### 3 Standard TV-norm: divider ratio 525 (60Hz) or 625 (50Hz)

When the system is switched to the narrow window (standard mode) it is checked whether the incoming vertical sync pulses are according to the TV norm, if so IVW=1. When 15 standard TV-norms are counted the divider system is switched to the standard divider ratio mode. In this mode the divider is always reset at the standard value even if the vertical sync pulse is missing.

The system switches back to the narrow window when 3 vertical sync pulses are missed. When also in the narrow window 3 vertical sync pulses are missed the divider will switch to the search window mode.

As described above the vertical divider needs some waiting time before switching back to the search window mode. When a fast reaction is required for instance during channel switching the system can be forced to the search window by means of I<sup>2</sup>C bus, setting **NCIN** = 1 (vertical divider mode). Immediate after forcing to search mode **NCIN** has to be set back to 0 for optimum performance.

The vertical synchronisation mode of operation can be selected by I<sup>2</sup>C bus, when no input signal is present ( $\mathbf{SL} = 0$ ), the vertical frequency is pending on the settings of **FORF/FORS** (**FOR**ced **F**ield frequency):

- 0.0 60 Hz when **SL** = 0, synchronizing on both 50 and 60 Hz input signals when available

- 0 1 60 Hz only, 60 Hz when **SL** = 0, synchronizing only from 54 to 64.5 Hz, for 60 Hz only environment, cannot synchronize on 50 Hz input signals (picture starts rolling)

- 10 Keep last detected, remains at vertical frequency of the input signal, present before **SL** becomes 0, synchronizes both on 50 and 60 Hz input signals. This mode is useful when both 50 and 60 Hz signals can be received but signal conditions are such that for short time signal (and synchronisation) is lost.

- 1 1 50 Hz when SL = 0, synchronizing on both 50 and 60 Hz input signals when available

Note that when **POC** is set to 1, **SL** is immediately forced to 0 and the vertical output will direct run on the frequency, selected by **FORF/FORS** for SL = 0.

Furthermore 50/60Hz identification is available by I<sup>2</sup>C bus **FSI** (50/60Hz), and norm signal identification with **IVW**.

#### \* Vertical output VA

The vertical divider generates an output pulse for further processing of the YUV signals and for display and deflection timing.

The pulse is positive and the rising edge starts 37.7 µs after the starting edge of the vertical synchronisation in the composite sync. The duration is 2.5 lines for 50 Hz signals and 3 lines for 60 Hz signals.

When for the horizontal pin 60 external clamp mode is selected (ECL = 1),  $V_A$  is suppressed.

A 2 : Block diagram: Horizontal and vertical synchronization

#### 2.2.3 Filters and Switches

See also the related block diagram A3 at page 37.

The main functions are:

- \* CVBS, Y/C signal selection.

- \* Filter calibration.

- \* Chrominance signal processing.

- \* Luminance signal processing.

- \* Y helper lines processing.

- \* YUV<sub>INT</sub> and RGB/YUV<sub>EXT</sub> selection.

#### \* CVBS, Y/C signal selection

The input selector has 3 CVBS inputs at pins 14, 16 & 18 and 2 Y/C inputs at pins 20, 21 & 23, 24 which can be selected via the I<sup>2</sup>C bus (**DEC3..0**); the Y/C inputs can also be used as additional CVBS inputs.

Two AV inputs are available which can be used for sensing 3 voltage levels on each pin, for instance to sense the status of pin 8 of SCART connectors. The status can be read out via I2C bus bits S1A, S1B and S2A, S2B.

For AUTO YC mode (Put **DEC3**=1), the input selector automatically detects whether a CVBS or Y/C signal has been supplied by monitoring the burst amplitude at pins 20, 21 if **DEC 3..0** is set = 1,1,0,0 (or pins 23, 24 if **DEC 3..0** is set = 1,1,1,0) once after sync lock; the larger burst signal has selection preference. The selection status can be checked with the status output bit **YC**; (note that during search mode for the colour system then **YC** = 1).

For application with combfilters:

- **ECMB** is set = 1; the subcarrier frequency  $F_{SC}$  with DC level of 4.2V is present at pin 30.

- SYS1, SYS2 outputs at pins 25, 27 is used to switch the comb filter to the different colour standards according to Table 4 .

The selected input signal is supplied to combfilter from pin 26. For PAL/NTSC signals, the combed Y/C outputs from the combfilter (supplied to the  $Y_{COMB}$ ,  $C_{COMB}$  inputs at pins 28, 29 respectively) are selected; for SECAM or BLACK-WHITE signals, the  $Y_{COMB}$ ,  $C_{COMB}$  inputs at pins 28, 29 will not be selected but instead the concerned CVBS or Y/C signal remains selected.

| Colour standard | SYS1 | SYS2 | Selected Xtal |

|-----------------|------|------|---------------|

| PAL-M           | 0    | 0    | C (3.575611)  |

| PAL-B,G,H,D,I   | 0    | 1    | A (4.433619)  |

| NTSC-M          | 1    | 0    | D (3.579545)  |

| PAL-N           | 1    | 1    | B (3.582056)  |

Table 4 : SYS1, SYS2 truth table

In AUTO COMB mode (**ECMB** and **DEC3** are both set = 1), the input selector automatically selects Y/C mode if larger burst is present at the C inputs (pins 21, 24) for all standards. If larger burst is present at the CVBS3, CVBS4 inputs then comb filter outputs (supplied to the  $Y_{COMB}$ ,  $C_{COMB}$  inputs at pins 28, 29 respectively) is selected however for SECAM or BLACK-WHITE signals (i.e. combing is not possible), the concerned CVBS signal remains selected.

The selection status whether  $Y_{COMB}$ ,  $C_{COMB}$  (pins 28, 29) is selected can be checked with the status output bit **CMB**. The three outputs (CVBSO<sub>TXT</sub>, CVBSO<sub>PIP</sub> and COMBCVBS) can be independently selected as shown in Table 5 to Table 7. This allows the features:

- displaying main and PIP CVBS signals independently,

- record select out,

- monitoring teletext from different source. In Y/C mode, the Y and C signals are added to form a CVBS signal and can be supplied to:

- the  $CVBSO_{TXT}$  output (**TXT2..0** = 1, 0, 1 or 1, 1, 1)

- the CVBSO<sub>PIP</sub> output (**PIP2..0** = 1, 0, 1 or 1, 1, 1) or

- the COMBCVBS output (refer to Table 5).

Note: The names are arbitrary in that it is possible to supply COMBCVBS signal to both combfilter and teletext decoder and supply  $CVSO_{TXT}$  signal to the SCART plug.

The input selector configuration is shown in Fig 9.

Fig 9 : Input selection

| ECMB | DEC3 | DEC2 | DEC1 | DEC0 | SELECTED   | COMBCVBS | CLOSED SWITCHES  |

|------|------|------|------|------|------------|----------|------------------|

|      |      |      |      |      | SIGNAL     | OUTPUT   | (refer to Fig 9) |

| 0    | 0    | 0    | 0    | X    | CVBSint    | CVBSint  | S1 S2 S5         |

| 0    | 0    | 0    | 1    | 0    | CVBS1      | CVBS1    | S6 S7 S10        |

| 0    | 0    | 0    | 1    | 1    | CVBS2      | CVBS2    | S11 S12 S15      |

| 0    | 0    | 1    | 0    | 0    | CVBS3      | CVBS3    | S16 S17 S20      |

| 0    | 0    | 1    | 0    | 1    | YC3        | Y3+C3    | S16 S20 S21 S24  |

| 0    | 0    | 1    | 1    | 0    | CVBS4      | CVBS4    | S25 S26 S29      |

| 0    | 0    | 1    | 1    | 1    | YC4        | Y4 +C4   | S25 S29 S30 S33  |

| 0    | 1    | 1    | 0    | 0    | auto YC3   | CVBS3 or | S16 S17 S20 or   |

|      |      |      |      |      |            | Y3+C3    | S16 S20 S21 S24  |

| 0    | 1    | 1    | 1    | 0    | auto YC4   | CVBS4 or | S25 S26 S29 or   |

|      |      |      |      |      |            | Y4 +C4   | S25 S29 S30 S33  |

| 1    | 0    | 0    | 0    | X    | YC COMB    | CVBSint  | S5 S34 S35       |

| 1    | 0    | 0    | 1    | 0    | YC COMB    | CVBS1    | S10 S34 S35      |

| 1    | 0    | 0    | 1    | 1    | YC COMB    | CVBS2    | S15 S34 S35      |

| 1    | 0    | 1    | 0    | 0    | YC COMB    | CVBS3    | S20 S34 S35      |

| 1    | 0    | 1    | 1    | 0    | YC COMB    | CVBS4    | S29 S34 S35      |

| 1    | 1    | 1    | 0    | 0    | auto COMB3 | CVBS3 or | S20 S34 S35 or   |

|      |      |      |      |      |            | Y3 +C3   | S16 S20 S21 S24  |

| 1    | 1    | 1    | 1    | 0    | auto COMB4 | CVBS4 or | S20 S34 S35 or   |

|      |      |      |      |      |            | Y4 +C4   | S25 S29 S30 S33  |

Table 5 : Input selection possibilities

| TXT2 | TXT1 | TXT0 | CVBSO<br>TXT | CLOSED SWITCHES<br>(refer to Fig 9) |

|------|------|------|--------------|-------------------------------------|

| 0    | 0    | X    | CVBSint      | S4                                  |

| 0    | 1    | 0    | CVBS1        | S9                                  |

| 0    | 1    | 1    | CVBS2        | S14                                 |

| 1    | 0    | 0    | CVBS3        | S19                                 |

| 1    | 0    | 1    | Y3 + C3      | S19 S23                             |

| 1    | 1    | 0    | CVBS4        | S28                                 |

| 1    | 1    | 1    | Y4 + C4      | S28 S32                             |

Table 6 : TXT output selection possibilities

| PIP2 | PIP1 | PIP0 | CVBSO<br>PIP | CLOSED SWITCHES<br>(refer to Fig 9) |

|------|------|------|--------------|-------------------------------------|

| 0    | 0    | X    | CVBSint      | S3                                  |

| 0    | 1    | 0    | CVBS1        | S8                                  |

| 0    | 1    | 1    | CVBS2        | S13                                 |

| 1    | 0    | 0    | CVBS3        | S18                                 |

| 1    | 0    | 1    | Y3 + C3      | S18 S22                             |

| 1    | 1    | 0    | CVBS4        | S27                                 |

| 1    | 1    | 1    | Y4 + C4      | S27 S31                             |

Table 7: PIP output selection possibilities.

#### \* Filter calibration

The filter calibration loop is an auto-tuning loop which calibrates every field retrace. The loop is stabilised when the resonant frequency of the cloche filter is Fsc (Fsc = VCXO reference signal which is at 4.4MHz or 3.6MHz depending upon which Xtal is selected).

The chroma bandpass and chroma trap filters are also controlled to Fsc. The chroma bandpass centre frequency can be set to 1.1Fsc via I2C bus command **CB**.

For SECAM reception the cloche resonant frequency is set to 4.286MHz and the chroma trap is shifted to 4.3MHz to ensure optimal subcarrier rejection.

#### \* Chrominance signal processing

For chroma signal processing, the selected signal is supplied to both the PAL/NTSC chroma bandpass filter and the SECAM cloche filter via a variable gain amplifier which is controlled by ACC and ACL detection circuits.

The dynamic range of the ACC is 26dB and detects only the burst amplitude; consequently the burst signal at the bandpass/cloche filter input is constant for a burst signal range +6dB -> -20dB where  $0dB = 300mV_{PP}$  burst.

The ACL is a chroma amplitude detector and is active when the chroma/burst ratio exceeds approximately 3. It ensures that CVBS signal to chroma bandpass & cloche filter is limited for large chroma/burst ratios (>3). which results in a constant saturation for such non-standard transmissions.

The ACL is independent of the ACC; it controls only the chroma amplitude and does not influence the colour burst sensitivity. The ACL function can be switched on/off via bus command **ACL**.

The output signal of the chroma bandpass circuit is supplied to the PAL/NTSC decoder and the output signal of the cloche filter is supplied to the SECAM decoder for further chroma processing.

For PALplus helper demodulation the chrominance signal at the input of the bandpass filter is used. This to insure sufficient bandwidth of the demodulated Y helper signal. Omitting the bandpass filter is not a problem here because the helper lines only contain chrominance information.

Application Note AN98072

#### \* Luminance signal processing

For luminance processing, the selected CVBS signal is first clamped and then supplied to the chroma trap circuit. The chroma trap is bypassed for no burst transmissions when in own intelligence mode (automode). For Y/C mode, the Y signal follows a direct path with 160ns delay so as to ensure similarity with chroma trap delay. Consequently the Y signal is supplied to an adjustable delay line (0ns - 440ns, minimum step is 40ns, controlled via bus bits YD3..0) and variable gain circuit (I2C bus bits GAI1 and GAI0) before being supplied to the YUV selection circuit.

#### \* Y helper lines processing.

For PALplus mode the decoded Y helper signal from helper decoder always follows the CVBS path with chroma trap to suppress the 4.43MHz restcarrier. The helper signal is multiplexed with the regular 430 letterbox lines luminance signal. Notice that the 430 letterbox lines luminance signal not only can follow the CVBS path with chroma trap (in case of a CVBS input signal) but also the Y/C path with 160ns delay line (in case of a Y/C signal or when selecting external digital MACP processing).

#### \* YUV<sub>INT</sub> and RGB/YUV<sub>EXT</sub> selection.

Two external linear RGB inputs with fast blanking possibility are available; fast blanking RGB2 has priority above fast blanking RGB1. The RGB1 inputs can also be used as YUV inputs (selectable via I2C bus). The RGB signals are converted to YUV signals and then fed to the YUV selection circuit. Here it is possible to insert the external signals in the internal YUV picture for OSD or PIP applications. The clamping of the RGB signals is normally done with an internal clamppulse, however if the external RGB signals are not synchronous with the internal YUV signals an external clamppulse has to be supplied via pin 60 HA/CLP output/input. See also page 26, \* Horizontal input/output.

TDA9321 H

TV Input Processor

Application Note

AN98072

A 3: Block diagram: Filters and Switches

Application Note AN98072

#### 2.2.4 Colour decoder

See also the related block diagram.

The main functions are:

- \* PLL/VCXO

- \* PAL/NTSC demodulation

- \* PALplus helper demodulation

- \* SECAM demodulation

- \* ASM (Automatic System Manager)

#### \* PLL/VCXO

The PLL operates during the burstkey period; it generates a VCXO reference signal (  $f_{VCXO}$  ), in phaselock with the incoming burst signal (  $f_{BURST}$  ).

Prior to lock condition, the signals  $f_{VCXO}$  and  $f_{BURST}$  are not synchronous and are present at phase detector input. The loop filter averages the phase detector output current and the resulting control signal to the VCXO is proportional to  $Sin(2\pi\Delta ft)$  where  $\Delta f = f_{VCXO} - f_{BURST}$ .

A lock situation occurs when  $\Delta f < VCXO$  holding range; once in lock, the phase detector output current is proportional to  $\Theta_E = \Theta_{VCXO} - \Theta_{BURST}$  ( $\Theta_E$  is the static phase error).

The combined phase detector and VCXO sensitivity is high to ensure a small static phase error.

For fast colour acquisition, the phase detector is in high gain mode when a colour system is not yet identified.

The VCXO loop (not to be confused with phase locked loop, PLL) compensates for any attenuation loss or phase shift in the crystal so that the it's loop gain is unity and loop phase shift is zero. The VCXO reference outputs (0° and 90°) are stable sinusoids.

VCXO oscillation is at series resonance of the selected Xtal. Since the PLL automatically tunes the VCXO to the burst (if inside the PLL holding range) fine tuning of the VCXO with a trimming capacitance is not necessary.

The motional capacitance of the Xtal is damped by the internal resistance of the VCXO pins (i.e. 1K) in order to realise the holding range.

The catching range (pull-in) of the PLL loop is governed by the PLL loop filter; the loop filter can be chosen so that PLL holding and catching range are similar (direct catching).

The HUE phase rotator is inoperational when the PLL is active (i.e no phase rotation during the burstkey period). Outside the burstkey period, the hue control rotates the VCXO reference phases from -40° to 40° linearly for I<sup>2</sup>C bus command (HUE: 0 --> 63), see also device specification.

#### \* PAL/NTSC demodulation

The  $0^{\circ}$  and  $90^{\circ}$  reference signals from the VCXO are supplied to the HUE phase rotator; it's outputs (H0, H90) are supplied to the (B-Y) and (R-Y) burst demodulators respectively.

The demodulated burst from the (B-Y) demodulator supplies NTSC ident information to the ASM (IDN signal).

The demodulated burst from (R-Y) demodulator supplies PAL ident information to the ASM (IDP signal).

For correct demodulation of (R-Y) PAL burst and chroma signals, then the H90 signal requires  $180^{\circ}$  phase shift on alternate lines. This is realised with the H/2 switch before the (R-Y) demodulator. It is not active during demodulation of NTSC signals.

The (B-Y)/(R-Y) baseband signals are obtained from the chroma signal by the (B-Y)/(R-Y) demodulators, filtered and supplied via the PAL/SECAM switch (PS) to the internal baseband delay line.

The demodulator gain ratio (B-Y)/(R-Y) is typically 1.78 in order to compensate for scaling in the transmitter.

For NTSC applications it is possible to bypass the delay line via I2C bus command **BPS**; the gain is also corrected then by a factor two.

The  $V_{INT}$  and  $U_{INT}$  signals from delay line outputs are fed to the YUV selection circuit (see YUV/RGB processing part).

PALplus has been developed to introduce wide screen transmissions with a backward compatibility for PAL 4:3 sets. A PALplus signal has the format of a standard analogue PAL composite signal, containing 430 PAL picture lines in letterbox format (lines 60 - 274 and 372 - 586), together with helper information hidden in the black bands above and below the visible letterbox area (lines 24 - 59, 336 - 371, 275 - 310, 587 - 622).

A viewer with a 4:3 TV set will see a letterbox picture: black bars of 1/8 picture height at the top as well as at the bottom with a 16:9 picture in between (see Fig 10a).

Fig 10: Possible PALplus picture displays

A wide screen TV set without PALplus decoder will show a picture as in Fig 10b, or when a zoom function is available, a picture as in Fig 10c, however with only 430 lines of vertical resolution.

When a wide screen TV set has a PALplus decoder, it expands the letterbox format to a full-size wide screen picture with a vertical resolution of 574 lines. The decoder uses the helper information, hidden within the black bars.

Furthermore a PALplus signal will deliver full luminance bandwidth when using a Y/C separation technique called: 'Motion Adaptive Colour Plus' (MACP). Using this technique the signal becomes free from cross colour and cross luminance. This algorithm requires MACP preprocessing in the PALplus encoder at the studio output.

This digital MACP processing takes place on the YUV signals.

Application Note AN98072

#### \* PALplus helper demodulation

The Y helper synchronous demodulator uses the chroma signal before the chroma bandpass to achieve sufficient bandwidth. This demodulator is active during the helper lines when  $\mathbf{HD} = \mathbf{1}$ . The correct B-Y demodulation axis can be adjusted via subaddress 03 (D5..D0).

The demodulated Y helper lines are multiplexed with the luminance letterbox lines (see Filters & Switches:

#### \* Y helper lines processing).

The PALplus parts which the TDA9321 H processes are in short:

- helper demodulation and multiplexing the helper signal with the letterbox luminance signal.

- chrominance trap bypassing if necessary.

- creation of reference line 22 (see Fig 11).

- creation of black set-up and helper set-up (see Fig 11).

- correct blanking and timing reference for the necessary PALplus post processing IC's.

In case of a PALplus input signal, the standard identification system of the TDA9321 H only determines PAL and needs additional I<sup>2</sup>C-bus information for PALplus processing via bus bits **MACP**, **HD**, **HOB** and **HBC**.

The **HD** bit (helper demodulation) enables PALplus helper demodulation on the U phase (i.e. the B-Y demodulation axis). The demodulated helper luminance signal is always led to the 4.43MHz notch filter.

is multiplexed with the regular 430 letterbox lines luminance signal and via the adjustable luminance delay line and YUV selection circuit supplied to the Y output. The black level of the luminance signal is internally clamped to the black level generated by the helper demodulator.

As there is only a 4.43MHz internal notch filter for the demodulated helper, an external notch filter is necessary to suppress the remaining 8.86MHz demodulation product. Using an internal low pass filter as used after the

(R-Y) and (B-Y) demodulators is not possible here on account of the high requirements needed for bandwidth and group delay of the helper luminance signal.

Bus bits **HD** and **MACP** also determine the presence of a black set-up voltage (with luminance scaling of a factor 0.8) and a helper set-up voltage for the demodulated helper signal on the Y output signal. These set-up voltages are necessary for PALplus signal post processing outside the TDA9321 H. The set-up voltages are also multiplexed into a reference line 22, used together with the demodulated helper reference of line 23 and luminance reference of line 623 both present in every PALplus signal for correct PALplus reference post processing. See Fig 11.

Additional helper blanking bits (**HOB**, **HBC**) determine whether the helper signal has to be blanked or blanked conditionally depending on the signal to noise ratio bit **SNR**. Helper blanking can only take place on a norm sync signal, indicated by output bit NRM = 1 (See also page 58, **HOB**: <u>Helper Output Blanking</u>).

The TDA9321 H can handle PALplus signals in either CVBS or Y/C format. In case of a Y/C signal the modulated helper must be available on one of the chrominance input pins. The use of the 4.43MHz trap will not be necessary then, as the chrominance and luminance component are already separated, so the 4.43MHz trap is bypassed for the letterbox luminance signal (not for the demodulated helper signal).

During helper demodulation the internal chroma bandpass filter is not used.

The signalling bits in line 23 (see Fig 11) are processed in the same manner as letterbox luminance lines. Signalling bit decoding and PALplus identification has to be done externally with the  $I^2C$  bus as communication link to the TDA9321 H via bus bits **MACP**, **HD**, **HOB** and **HBC**.

Fig 11: PALplus CVBS input and Y output signals

#### \* SECAM demodulation

SECAM demodulation is realised with a PLL type demodulator.

If a 4.43MHz Xtal is present on pin 54 then SECAM demodulation is possible. The auto tuning loop, consisting of PLL demodulator and oscillator, ensures that the PLL oscillator is locked to the 4.43MHz Xtal frequency during calibration time in the vertical retrace period. The SECAM reference voltage, generated at pin 16, is regulated in order that the PLL demodulator output is set to a reference voltage derived from an internal stable bandgap voltage.

Outside calibration the oscillator remains tracking the SECAM chrominance resulting in the corresponding demodulated voltage. This is delivered to the LF de-emphasis stage and to the line ident stage of the Automatic System Manager (IDS signal). The H/2 switch distributes the demodulated signal to the (R-Y) and (B-Y) amplifiers and via the PAL/SECAM switch (PS) to the baseband delay line.

The V<sub>INT</sub> and U<sub>INT</sub> signals from delay line outputs are fed to the YUV selection circuit (see Filters & Switches).

#### \* ASM (Automatic System Manager)

The ASM is field synchronous; it can identify PAL/NTSC/SECAM colour standards. The different possibilities are controlled by the I<sup>2</sup>C bus input commands (CM3, CM2, CM1, CM0). These input commands are communicated to the ASM via the I<sup>2</sup>C bus.

The I<sup>2</sup>C bus input commands (**XD**, **XC**, **XB**, **XA**), also supplied to the ASM via the I<sup>2</sup>C bus, indicate which Xtals are connected to pins 54, 55, 56, 57. This is also essential for correct calibration of the horizontal oscillator.

For colour identification purposes there is also communication with the ASM and:

- the PAL/NTSC ident circuits (IDP, IDN)

- the SECAM ident (IDS)

- the VCXO via Xtalswitch (XTS)

- the PAL/SECAM switch (PS)

- the R-Y demodulator (H/2)

The I<sup>2</sup>C output commands (SXD, SXC, SXB, SXA) indicate whether the (XD, XC, XB, XA) bits have been correctly transmitted by the I<sup>2</sup>C bus. The I<sup>2</sup>C output commands (CD3, CD2, CD1, CD0) indicate which colour system has been identified.

A 4: Block diagram: Colour decoder

## 2.2.5 I2C bus description

## 2.2.5.1 Overview I2C bits

For easy control, most functions of the TDA9321 H are controlled via the I<sup>2</sup>C bus:

| Input functions <sup>1)</sup> | Sub    | Data bits | are control | eca via tii | er e ous. |      |      |      |      |

|-------------------------------|--------|-----------|-------------|-------------|-----------|------|------|------|------|

| (write)                       | addr.  | Data Olts |             |             |           |      |      |      |      |

| (WITE)                        | (hex)  |           |             |             |           |      |      |      |      |

|                               | (IICX) | D7        | D6          | D5          | D4        | D3   | D2   | D1   | D0   |

| Colour decoder 0              | 00     | CM3       | CM2         | CM1         | CM0       | XD   | XC   | XB   | XA   |

| Colour decoder 1              | 01     | MACP      | HOB         | HBC         | HD        | 0    | ACL  | СВ   | BPS  |

| Luminance                     | 02     | 0         | 0           | GAI1        | GAI0      | YD3  | YD2  | YD1  | YD0  |

| Hue control HUE               | 03     | 0         | 0           | A5          | A4        | A3   | A2   | A1   | A0   |

| Spare                         | 04     | 0         | 0           | 0           | 0         | 0    | 0    | 0    | 0    |

| Synchronisation 0             | 05     | FORF      | FORS        | FOA         | FOB       | 0    | VIM  | POC  | VID  |

| Synchronisation 1             | 06     | 0         | 0           | 0           | 0         | BSY  | НО   | EMG  | NCIN |

| Spare                         | 07     | 0         | 0           | 0           | 0         | 0    | 0    | 0    | 0    |

| Video switches 0              | 08     | 0         | 0           | 0           | ECMB      | DEC3 | DEC2 | DEC1 | DEC0 |

| Video switches 1              | 09     | 0         | PIP2        | PIP1        | PIP0      | 0    | TXT2 | TXT1 | TXT0 |

| RGB switch                    | 0A     | 0         | 0           | 0           | 0         | YUV  | ECL  | IE2  | IE1  |

| Output pin switches           | 0B     | 0         | 0           | 0           | 0         | 0    | 0    | OS1  | OS0  |

| Vision IF                     | 0C     | FFI       | IFO         | GD          | MOD       | AFW  | IFS  | STM  | VSW  |

| Tuner take-over               | 0D     | 0         | 0           | A5          | A4        | A3   | A2   | A1   | A0   |

| Adjustment IF PLL             | 0E     | L'FA      | A6          | A5          | A4        | A3   | A2   | A1   | A0   |

| Output (read)                 |        | Data bits |             |             |           |      |      |      |      |

| Status byte 0                 | 00     | POR       | X           | X           | X         | SNR  | FSI  | SL   | IVW  |

| Status byte 1                 | 01     | CD3       | CD2         | CD1         | CD0       | SXD  | SXC  | SXB  | SXA  |

| Status byte 2                 | 02     | IN1       | IN2         | CMB         | YC        | S2A  | S2B  | S1A  | S1B  |

| Status byte 3                 | 02     | ID3       | ID2         | ID1         | ID0       | IFI  | PL   | AFA  | AFB  |

Table 8 : Condition PHI-1 loop

Note: All not-used bits should be set to zero, for compatibility with future devices.

# Application Note AN98072

For quick reference are all bits listed in alphabetical order in the two tables below. The bits are split up for control functions and analogue control.:

The meaning of the different colums in the table are:

#### Control bits table:

CONTROL BIT The short name for the control bit FUNCTION A short functional description REG The register subadress in HEX.

BIT The bit number (D7..D0) in the register

I/O Input or Output, Input = control bit, Output = status bit

MACRO The device macro, where the bit is related to:

IF: Vision IFSound: Sound part

Sync: Horizontal and Vertical synchronisation

Geo: Geometry (vertical & horizontal) and drive of vertical deflection

Filt/Sw: Filters and CVBS/Y/C switches

Col.Dec.Colour decoder

RGB: RGB output, input and control

FU Function class, the bits are divided in 5 classes:

SU Start-Up, bit has to be set correct before switching on from stand-by.

AL Alignment, bit(s) have to be aligned during production, the found values are set each

time before switching on from stand-by

SC Setmaker Control, bits which have to be controlled by the setmaker during operation for

correct performance like PHI-l loop time constant, positive modulation, etc.

UC User Control, bits which are normally accessible for the customer like contrast,

brightness, etc.

TK Tool Kit, bits which can help to improve performance under difficult working

conditions like RF phase modulation, wrong burst/chroma ratio, etc.

## Analog control:

Most colums are identical. The deviating colums:

STEPS The number of steps, available for this analogue function

RANGE The control range of the analogue control.

Survey control bits, in alfabetical order of their abbriviated name

| CONTROL BIT | FUNCTION                                                                                                                                        | REG | BIT     | I/O | MACRO    | FU |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|----------|----|

| ACL         | Automatic Colour Limiting, 1=on                                                                                                                 | 01  | 2       | I   | Filt/Sw  | TK |

| AFA, AFB    | AFC outputs                                                                                                                                     | 03  | 1,0     | О   | IF       | SC |

| AFW         | AFC Window, 1=275 kHz                                                                                                                           | 0C  | 3       | I   | IF       | SC |

| BPS         | ByPaSs base band delay line, 1=bypassed                                                                                                         | 01  | 0       | I   | Col.Dec. | SC |

| BSY         | Blanked Sync on Y-output, 1 = blanked                                                                                                           | 06  | 3       | I   | Filt/Sw  | SC |

| СВ          | Centre frequency chroma Bandpass, 0=centre freq.=Fsc, 1=centre freq.=1.1 Fsc                                                                    | 01  | 1       | I   | Filt/Sw  | SC |